2種のFPGAと2種のPMICを搭載

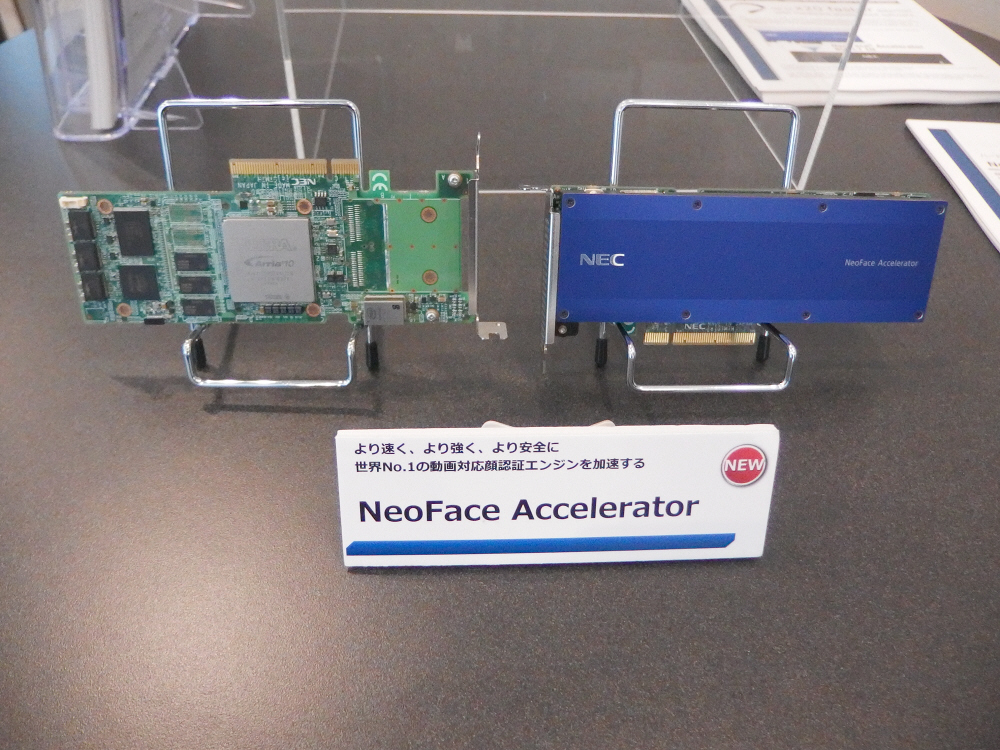

インテル系のイベントでの講演のせいか、阿部氏は「Intelのチップを沢山使っています」と前置きして、今回のアクセラレーターの基板写真と、そこに載っているIntel製のチップを紹介した。顔検出処理を担うFPGAのArria 10、今回のアクセラレーター全体を制御するFPGAのMAX 10、そしてFPGA電源向けの制御IC「EM 2130」と「EN 2342」を搭載しているとのことだった。

FPGAに実装したことで、顔検出処理はMPU上のソフトウエア処理に比べて20倍高速になった。顔認証処理全体(残りの3処理はMPU上のソフトウエア処理)では、全部をMPUでソフトウエア処理した場合に比べて4倍以上高速化した。

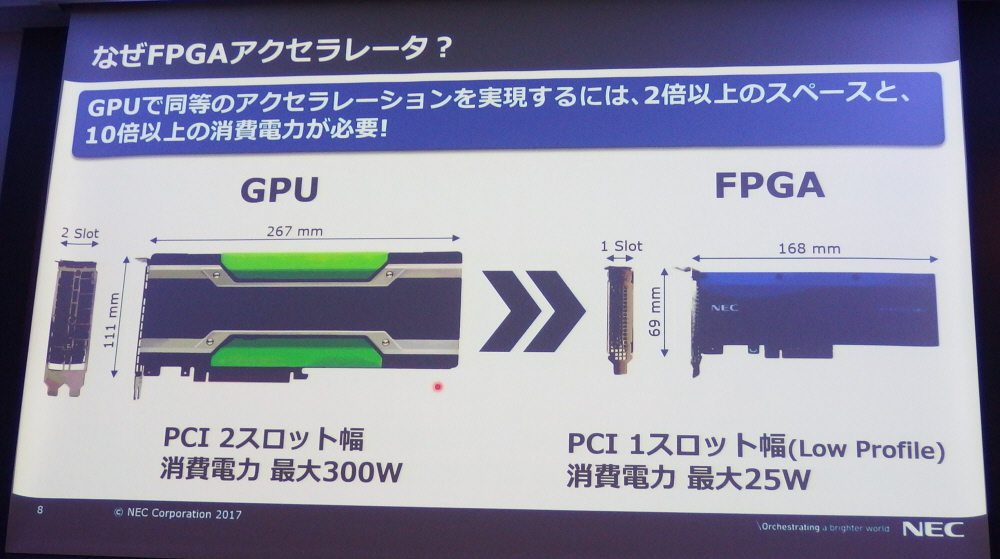

高速化と共に低消費電力化や小型化も達成したという。NECではGPU(米NVIDIA製品)ベースのアクセラレーターも検討していたが、今回のアクセラレーターよりも消費電力が10倍以上大きく、必要なPCIスロット数が多く、ボードの面積も大きくなってしまった。

今回のアクセラレーターの大きさは69mm×168mmで、LowプロファイルのPCIスロットを1つ(PCI Express Gen 3 ×4レーン)使う。写真では分かりにくいが、実物は「かなり小さい」という印象である。消費電力は最大25Wという。

現在、同社は、もう1つの重い処理である「特徴量計算」向けのアクセラレーターの開発を進めている。こちらのアクセラレーターが完成すると、NeoFaceの顔認証処理は、Xeonサーバーがなくても、エッジ側でほぼ完結するという。例えば、監視カメラ出力の後処理とネットワーキングを担う簡便な機器に、2つのアクセラレーターと一般的なプロセッサーICを搭載して、顔認証処理を行うようになるとのことだった。

.jpg)

.jpg)

.jpg)

.jpg)

コメントする コメントに関する諸注意(必ずお読みください)